Logické obvody #

Kombinačné obvody #

Pred kreslením logických obvodov musíme inicializovať knižnicu makier log_init. Knižnica obsahuje makrá pre kreslenie základných kombinačných a sekvenčných obvodov. Hradlá kombinačných logických obvodov môžu mať niekoľko vstupov, ich počet definujeme pomocou parametra n.

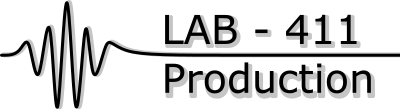

AND_gate(3) NAND_gate(3) OR_gate(2) NOR_gate(3) NXOR_gate(2)

NOT_gate() BUFFER_gate()

Zobrazenie hradiel kombinačné logických obvodov s variabilným počtom vstupov (and, nand, or, nor, xor), Obr. 102:

Obr. 102 Hradlá kombinačných logických obvodov.#

Definície makier pre hradlá s n vstupmi:

AND_gate (n, [N][B], [wid, [ht]])

OR_gate (n, [N][B], [wid, [ht]])

NOR_gate (n, [N|B],, [wid, [ht]])

NAND_gate(n, [N][B], [wid, [ht]])

NXOR_gate(n, N, [wid, [ht]])

parametre:

n - počet vstupov hradla

N - negované vstupy

B - zobrazenie hradla ako bloku podľa IEEE Standard 91-1984

wid - šírka

ht - výška

atribúty:

In1 ... InN - poloha vstupov

Out - poloha výstupu

N_Out - poloha stredu negovaneho vystupu (kružnice)

Definície makier pre hradlá s jedným vstupom (invertor, buffer):

NOT_gate(linespec,[B][N|n],wid,height, attributes)

BUFFER_gate(linespec, [N|B], wid, ht, [N|P]*, [N|P]*, [N|P]*, attributes)

parametre:

linespec - dĺžka a umiestnenie rezistora

N - negovaný vstup

B - zobrazenie ako bloku podľa IEEE Standard 91-1984

n - (písmeno) výmena negácie z výstupu na vstupe (pri NOT)

wid - šírka

ht - výška

atribúty:

ak je definovaný parameter linespec, hradlá majú atribúty

ako dvojpóly (.start, .centre, .end), inak

In1 - poloha vstupu

Out - poloha výstupu

C - stred hradla

NE - prívod napájania (VCC)

SE - prívod napájania (GND)

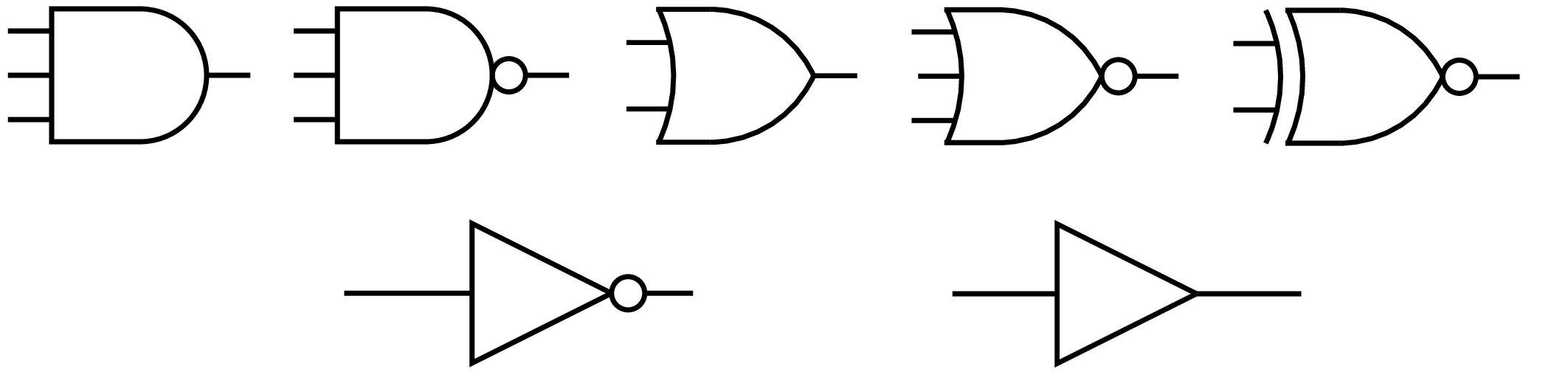

Pri kreslení logických obvodov je vhodné najskôr porozkladať hradlá po ploche a potom ich postupne prepájať. Na zjednodušenie prepojenia vývodov hradiel môžeme použiť jednoduché makro conn() s dvoma parametrami, ktoré sú súradnicami koncových bodov prepojenia. Zapojenie jednoduchého multiplexera je na obrázku Obr. 103:

define(`conn', `

line from $1 left_ (($1 - $2)/2).x;

line up_ to (Here.x, $2.y) then to $2;

')

G1: AND_gate(2) at (5, 2); "\sf G1" at G1.n above;

G2: AND_gate(2) at (5, 0.5); "\sf G2" at G2.n above;

G3: OR_gate(2) at (7, (G1.c.y + G2.c.y)/2 ); "\sf G3" at G3.n above;

G4: NOT_gate() at (3.5, 2.5); "\sf G4" at G4.n above;

conn(G3.In1, G1.Out)

conn(G3.In2, G2.Out)

conn(G1.In1, G4.Out)

line from G4.In1 left_ 0.35; DT: dot; line left_ 0.5; "\sf Q" at last line.end rjust;

line from G1.In2 to (LL.end.x, G1.In2.y); "\sf D1" at last line.end rjust;

line from G2.In2 to (LL.end.x, G2.In2.y); "\sf D0" at last line.end rjust;

line from G2.In1 to (DT.x, G2.In1.y) then to DT;

line from G3.Out right_ 1; "\sf Y" at last line.end ljust;

Sekvenčné obvody #

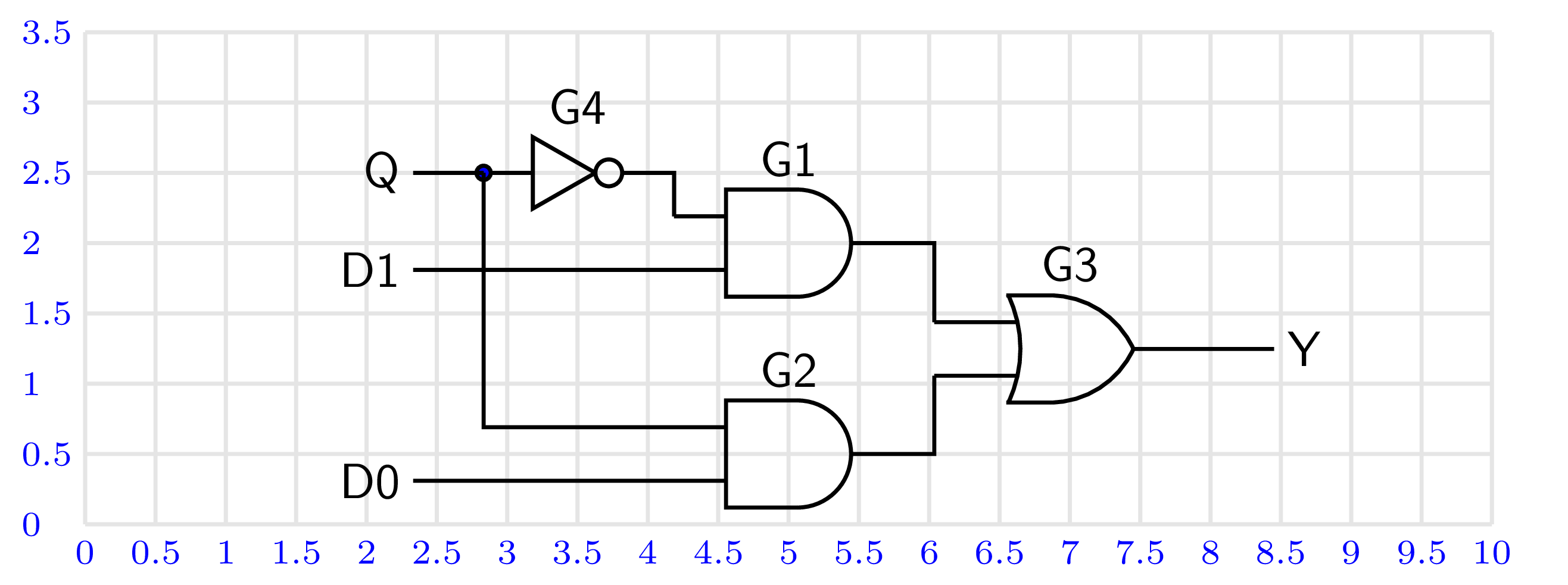

Základné typy sekvenčných obvodov (D, T, RS, JK) sú definované pomocou makra FlipFlop(), Obr. 104:

FlipFlop(D,Q1) FlipFlop(T,Q2) FlipFlop(RS,Q3) FlipFlop(JK)

Obr. 104 Zobrazenie typických sekvenčných obvodov.#

Definícia makra FlipFlop() má tvar:

FlipFlop(type, label, boxspec, pinlength)

parametre:

type - typ obvodu D|T|RS|JK

label - označenie obvodu

boxspec - parametre značky ako pre box

pinlength - dĺžka pinu

atribúty:

podľa mena pinu .D .CK .Q .NQ .R .S .J .K .PR .CLR

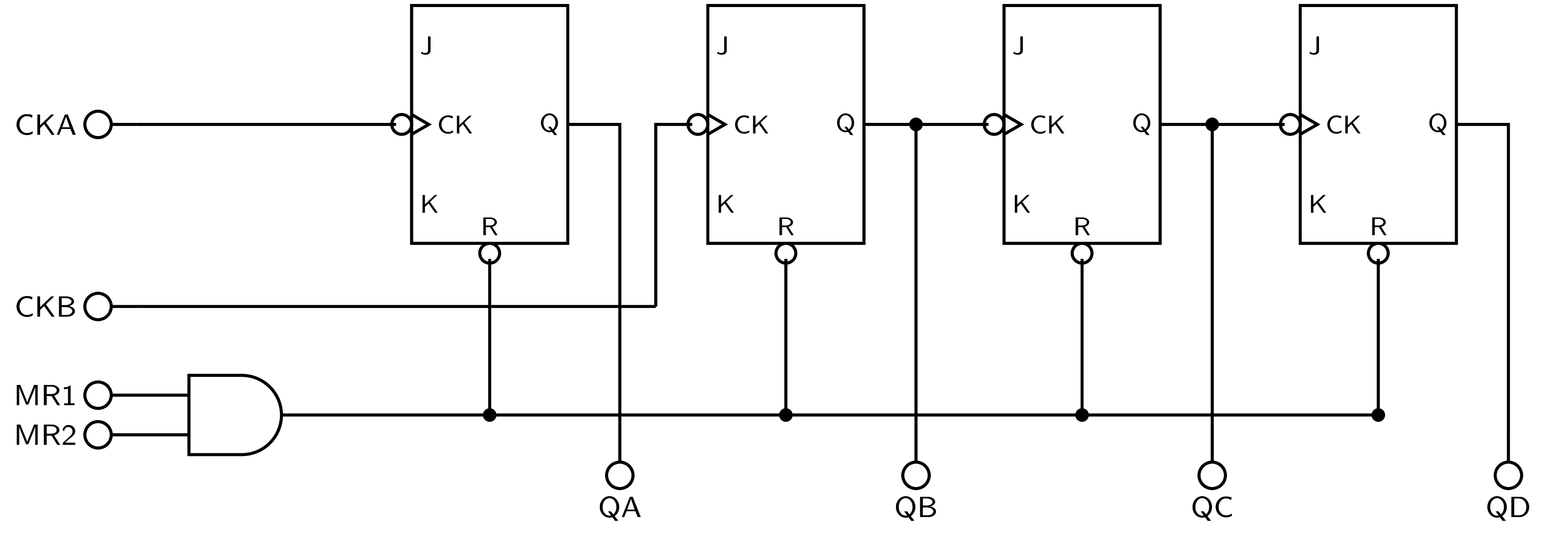

Pre vytváranie vlastných značiek obvodov môžeme použiť makrá popísané v kapitole Integrované obvody alebo makro FlipFlopX(), podrobný popis je v dokumentácii. Na obrázku Obr. 105 je zobrazené použitie nového makra JK93() v zapojení zobrazujúcom vnútornú štruktúru časovača 7493:

# JK obvod v strukture citaca 7493

define(`JK93', `[

BX:box wid 1.5 ht 6*lg_pinsep;

lg_pin(BX.nw - (0, 1*lg_pinsep), J, PinJ, w, ,0);

lg_pin(BX.nw - (0, 3*lg_pinsep), CK, PinCK, wEN,,0);

lg_pin(BX.nw - (0, 5*lg_pinsep), K, PinK, w, ,0);

lg_pin(BX.ne - (0, 3*lg_pinsep), Q, PinQ, e, ,0);

lg_pin(BX.s , R, PinR, sN, ,0 )

]')

Obr. 105 Vnútorné zapojenie čitača 7493 podľa TI (TODO-ODKAZ).#

Zbernice #

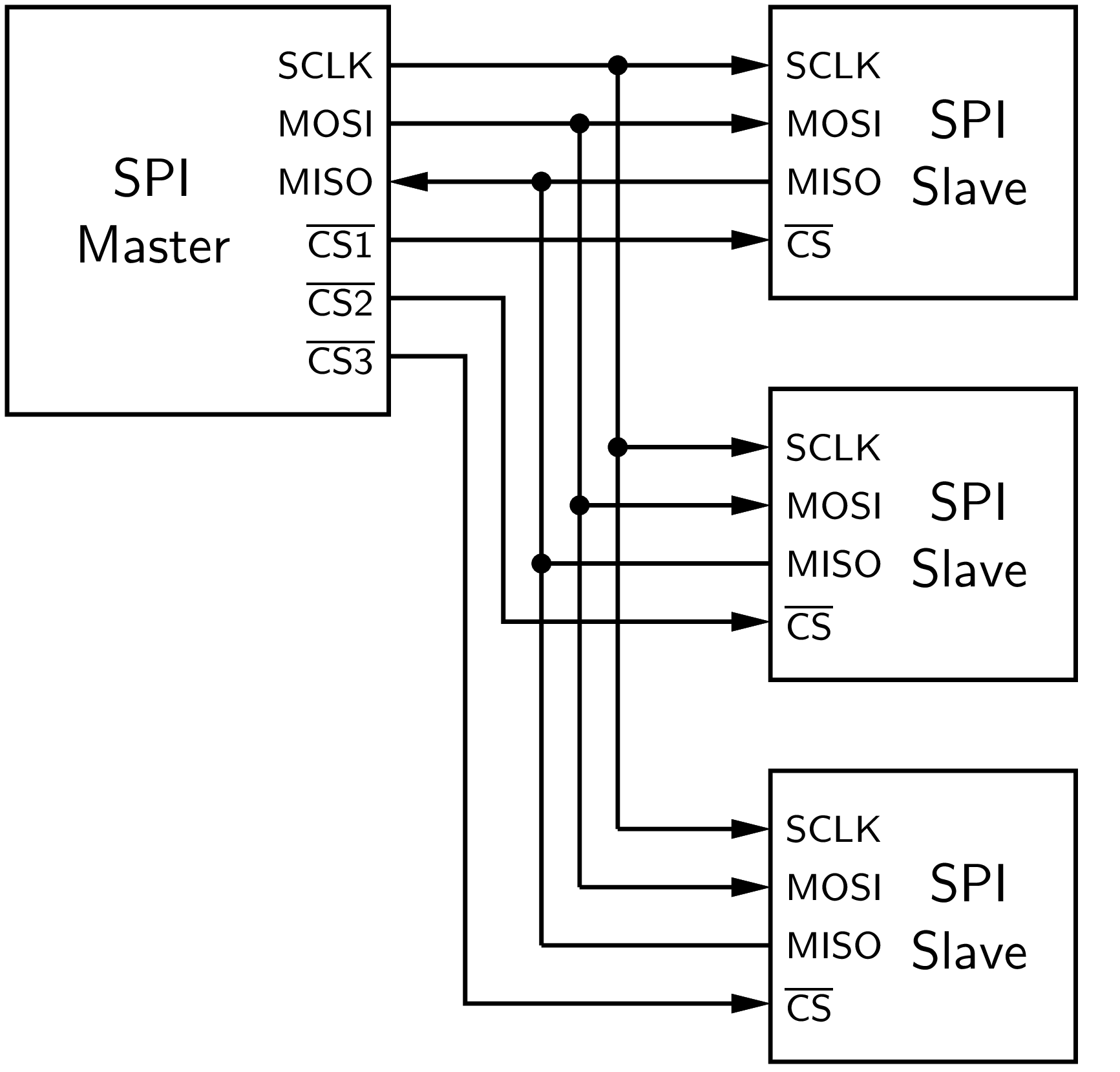

Digitálne systémy vo svojej architektúre často využívajú hierarchické usporiadanie obvodov do skupín zdielajúcich spoločný komunikačný systém, zbernicu. Rozkreslenie zbernice na jednotlivé vodiče môže byť niekedy neprehľadné, tak ako to ukazuje obrázok Obr. 106.

Obr. 106 Blokové zapojenie SPI zbernice v režime MDP (Multidrop).#

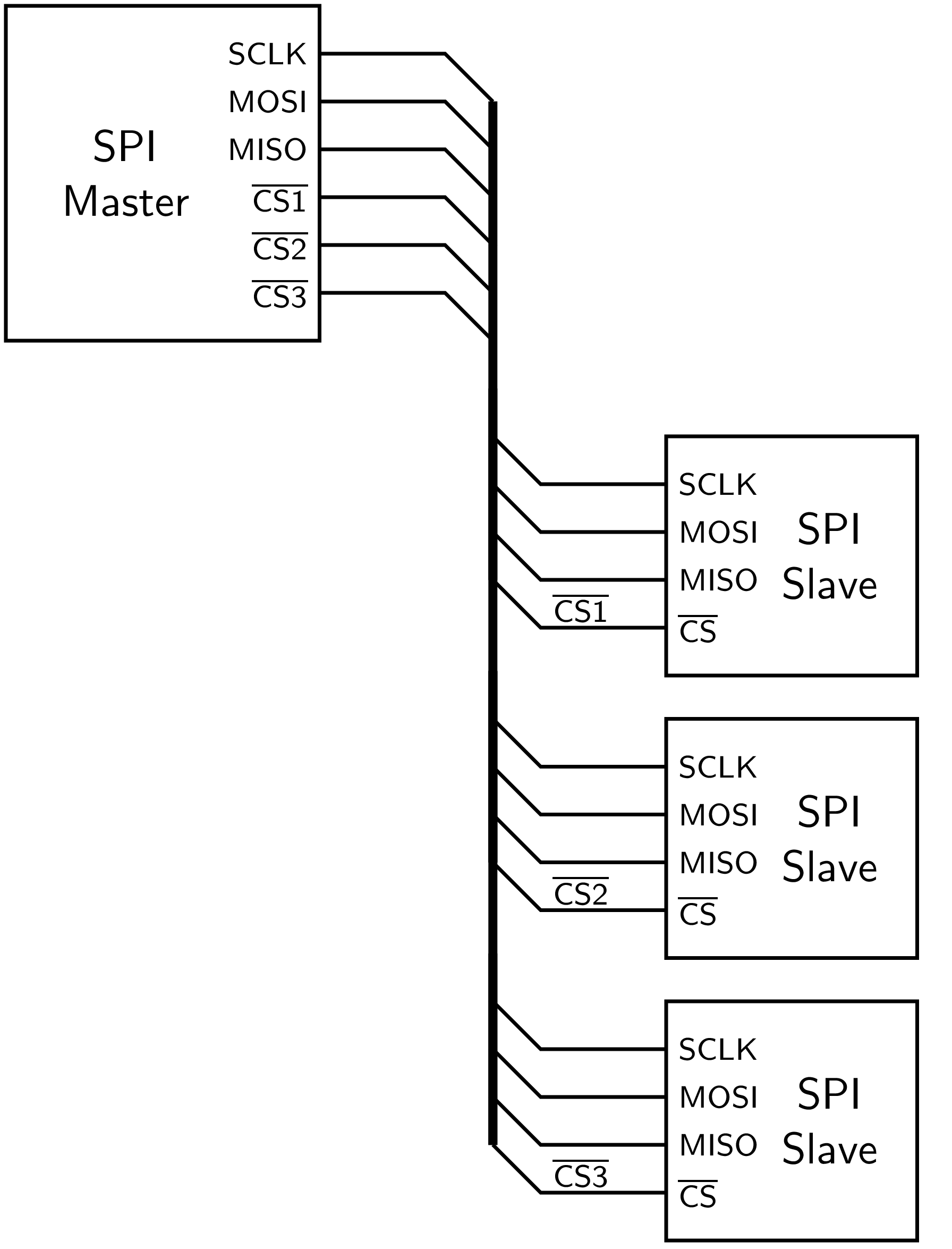

Použitím zberníc môžeme celé zapojenie zjednodušiť a sprehladniť, Obr. 107.

Obr. 107 Zapojenie SPI rozhrania pomocou vykreslenia zbernice.#

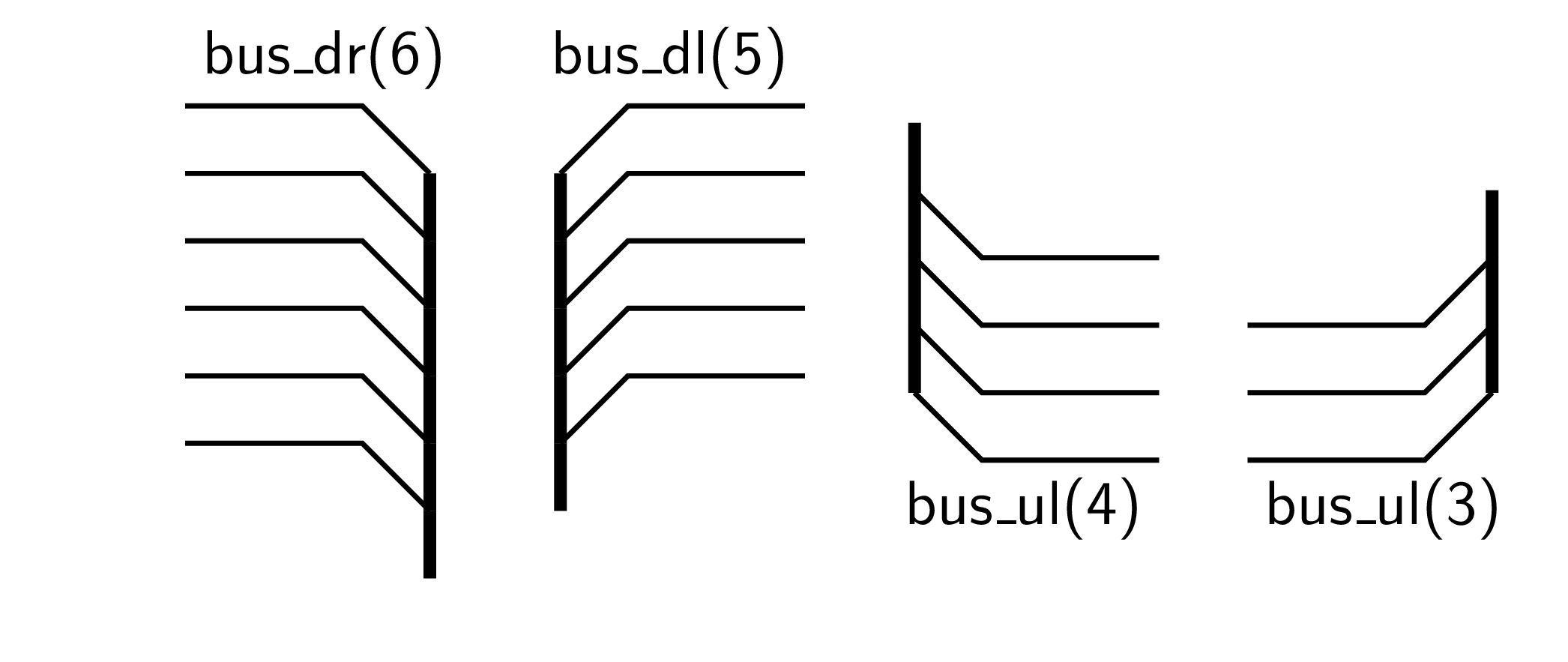

Zbernice môžeme pripájať k obvodom pomocou konektorov definovaných makrami v súbore lib_bus.ckt. Parametrom makier je počet vodičov zbernice, pomocou ďaľších makier môžeme popisovať jednotlivé vetvy zbernice ako aj ziskať referenciu na koniec každej vetvy, Obr. 108.

Obr. 108 Makrá pre kreslenie pripojenia zbernice k obvodu.#

Každý konektor zbernice má vetvy číslované od začiatku zbernice. Číslovanie vetiev je nezávislé od číslovania pinov pripojeného obvodu. Definícia makier pre pripojenie zbernice k obvodu má tvar:

bus_dl(n,d) - makra pre pripajanie zbernice k obvodom

bus_dr(n,d)

bus_ul(n,d)

bus_ur(n,d)

parametre:

n - počet vetiev

d - dĺžka vetvy

atribúty:

REF - poloha referenčného pinu č.1

START - začiatok zbernice

END - koniec zbernice

DOC - pozícia pre popisovanie zbernice

Pomocné makrá pre popis zbernice, polohu koncového bodu vetvy majú tvar:

bus_txl(bus, text, pin) - makrá pre popis vetvy zbernice, zarovnanie doľava

bus_txr(bus, text, pin) - zarovnanie doprava

bus_ref(bus, pin) - poloha koncovej vetvy zbernice

bus_conn(bus1, bus2) - spojenie zberníc úsečkou

parametre:

bus - referencia na zbernicu

text - popis, bez úvodzoviek

pin - čislo pinu zbernice

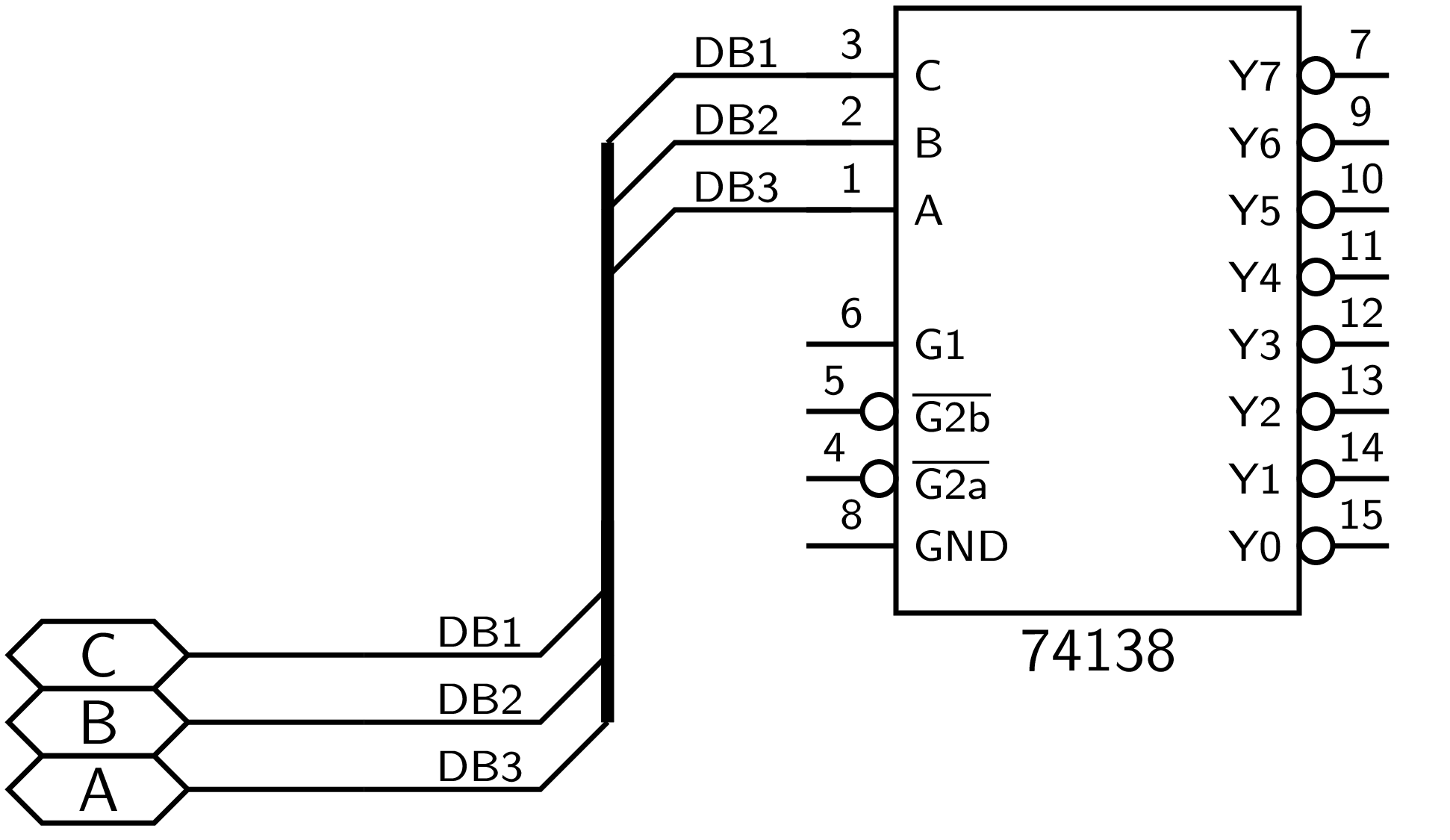

Pri pripájaní zberníc k obvodu využijeme konštrukciu with … at …. Koniec prvej vetvy konektoru je prístupný pod atribútom REF, ktorý pripojíme k zvolenému pinu obvodu, Obr. 109:

IC: IC74138(); "74138" at IC.s below;

B1: bus_dl(3) with .REF at IC.Pin3;

B2: bus_ur(3) with.END at B1.END+(0,-1)

bus_conn(B1,B2)

line left_ 1 from bus_ref(B2,1); tbox(A,,lg_pinsep,<>)

line left_ 1 from bus_ref(B2,2); tbox(B,,lg_pinsep,<>)

line left_ 1 from bus_ref(B2,3); tbox(C,,lg_pinsep,<>)

Obr. 109 Pripojenie zbernice k obvodu. ``#